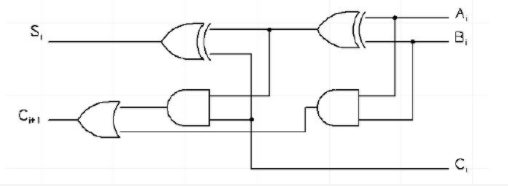

The figure below shows the i $^{th}$ full-adder block of a binary adder circuit. C${_i}$ is the input carry and C${_i}{_+}{_1}$ is the output carry of the circuit. Assume that each logic gate has a delay of 2 nanosecond, with no additional time delay due to the interconnecting wires. If the inputs A${_i}$,B${_i}$ are availble and stable throughout the carry propogation, the maximum time taken for an input C${_i}$ to produce a steady-state output C${_i}{_+}{_1}$ is $\_\_\_\_$ nanosecond.