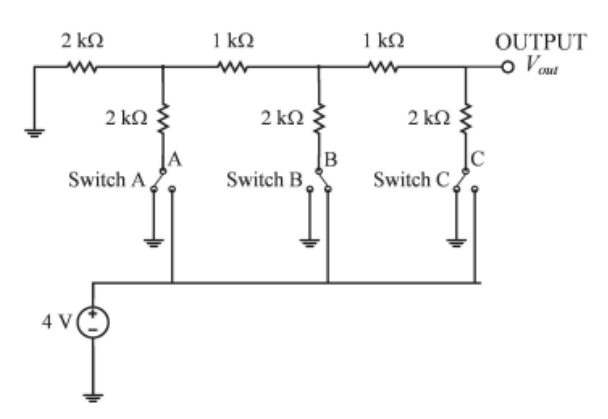

A resistor ladder digital-to-analog converter $\text{(DAC)}$ receives a digital input that results in the circuit having the state as shown in the figure. For this digital input, the Thevenin voltage, $V_{th},$ and Thevenin resistance, $R_{th},$ as seen at the output node are _________

- $V_{th} = 0.5 \; \text{V}, R_{th} = 1 \; \text{k}\Omega$

- $V_{th} = 0.5 \; \text{V}, R_{th} = 2 \; \text{k}\Omega$

- $V_{th} = 1 \; \text{V}, R_{th} = 1 \; \text{k}\Omega$

- $V_{th} = 1 \; \text{V}, R_{th} = 2 \; \text{k}\Omega$